High-speed Low-power Pipeline A/D Converters

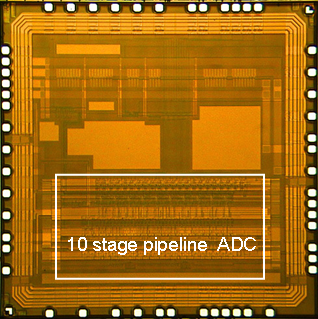

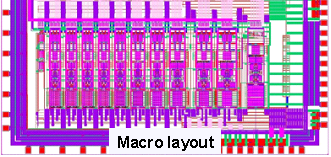

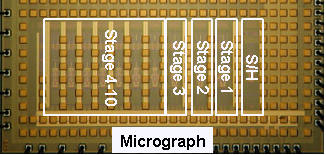

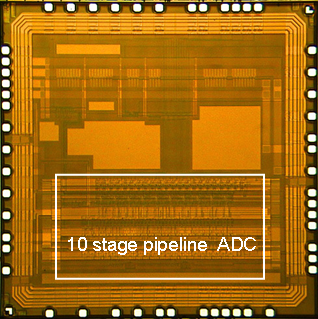

High-speed Low-power Pipeline A/D Converters are investigated as a key device of imaging and communication systems. The developed 10bit 30MSample/s ADC using a pseudo-differential architecture has achieved the lowest power dissipation of 16mW at 2.0 V supply voltage[1].

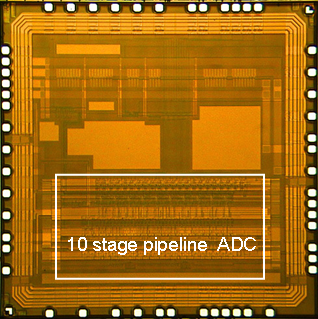

A 10bit 100MSample/s pipeline A/D converter which consumes 30mW at 1.0V supply voltage is also developed[2].

|

|

| 16mW 10bit 30MSample/s Pipelined A/D Converter

| 1V 30mW 10bit 100MSample/s Pipelined A/D Converter

|

References

- D. Miyazaki, M. Furuta, and S. Kawahito, "A 16mW 30Msample/s 10b Pipelined A/D Converter Using Pseudo Differential Architecture", Dig. of Tech. Papers, IEEE Int. Solid-State Circuits Conf., no.10.5, pp.174-175,Feb. 2002.

- D. Miyazaki, S. Kawahito, and M. Furuta, "A 10-b 30-MS/s Low-Power Pipelined CMOS A/D Converter Using a Pseudodifferential Architecture", IEEE Journal of Solid-State Circuits, Vol.38, No.2, pp.369-373, 2003.

- K. Honda, F. Masanori, and S. Kawahito, "A 1V 30mW 10b 100MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques", Proc. 2006 Symp. on VLSI Circuits, 25.4, Pp.276-277, Jun.2006.

- K. Honda, M. Furuta, and S. Kawahito, "A Low-Power Low-Voltage 10-bit 100-MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques", IEEE Journal of Solid-State Circuits, Vol.42, No.4, pp.-, 2007.

[Home] / [Research project]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: webmaster@idl.rie.shizuoka.ac.jp