画像圧縮集積イメージセンサ

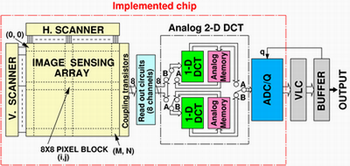

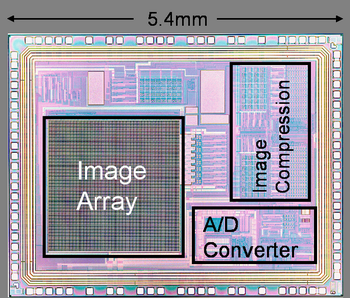

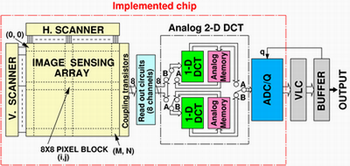

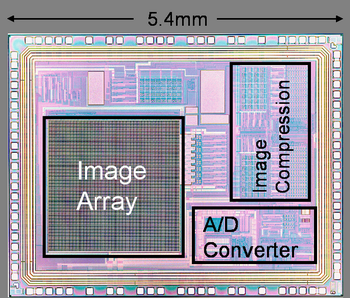

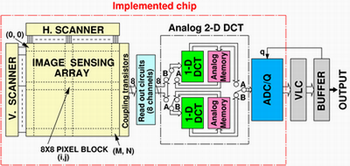

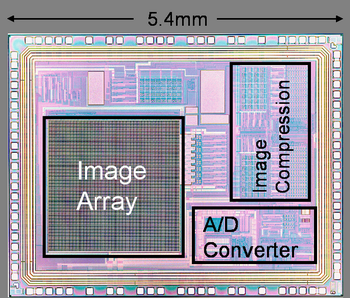

CMOSイメージセンサ上で画像圧縮を行うことで、超小型低消費電力のカメラモジュールを実現するワンチップカメラデバイスを開発しました。アナログ回路により2次元離散コサイン変換を実現しています。カプセル内視鏡等への応用を目指しています。1997年度のISSCCで発表しました。

|

|

| 処理回路のブロック図

| 試作イメージセンサチップ

|

文献

- S. Kawahito, M. Yosihda, M. Sasaki, K. Umehara, D. Miyazaki, Y. Tadokoro, K. Murata, S. Doushou and A. Matsuzawa," A CMOS image sensor with analog two-dimensional DCT-based compression circuits for one-chip camera", IEEE J. Solid-State Circuits, Vol.32, No.12, pp.2030-2041, Dec.1997.

- S. Kawahito, M. Yoshida, M. Sasaki, K. Umehara, Y. Tadokoro, K. Murata, S. Doushou and A. Matsuzawa, "A compressed digital output CMOS image sensor with analog 2-D DCT processors and an ADC/Quantizer", Dig. Tech. Papers, IEEE Int. Solid-State Circuits Conf., pp.184-185, Feb. 1997.

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: webmaster@idl.rie.shizuoka.ac.jp